Difference between revisions of "Interrupt"

m (→Interrupt controllerens opbygning) |

m (→Uden interrupt) |

||

| (2 intermediate revisions by the same user not shown) | |||

| Line 4: | Line 4: | ||

===Uden interrupt=== | ===Uden interrupt=== | ||

| − | :CPU’en spørger med intervaller om ydre enheder har brug for CPU’ens service. Dette kaldes at polle ydre enheder. Dette princip bevirker at CPU’en bruger overflødig tid, på at | + | :CPU’en spørger med intervaller om ydre enheder har brug for CPU’ens service. Dette kaldes at polle ydre enheder. Dette princip bevirker at CPU’en bruger overflødig tid, på for eksempel at "polle" tastaturet om der er trykket på en tast. |

| + | {{technote|heading=Bemærk|Ved pollning af flere ydre enheder, kan softwaren nemt blive meget rodet}} | ||

| + | |||

===Med interrupt=== | ===Med interrupt=== | ||

:Interrupt drevet. Dette bevirker at CPU’en arbejder uforstyrret af ydre enheder, indtil en ydre enhed ønsker at blive serviceret. Når en ydre enhed ønsker CPU’ens opmærksomhed afbryder den midlertidigt CPU’ens nuværende opgave, for at servicere den ydre enhed. Dette bevirker at CPU’en aflastes fra resultatløse forespørgsler til tastatur, mus, lydkort, harddisk, printer…… | :Interrupt drevet. Dette bevirker at CPU’en arbejder uforstyrret af ydre enheder, indtil en ydre enhed ønsker at blive serviceret. Når en ydre enhed ønsker CPU’ens opmærksomhed afbryder den midlertidigt CPU’ens nuværende opgave, for at servicere den ydre enhed. Dette bevirker at CPU’en aflastes fra resultatløse forespørgsler til tastatur, mus, lydkort, harddisk, printer…… | ||

| Line 32: | Line 34: | ||

{| | {| | ||

|- | |- | ||

| − | |[[Image:Interrupt PCold2.png| | + | |[[Image:Interrupt PCold2.png|400px|left|Interrupt controllerens opbygning]] |

|- | |- | ||

|} | |} | ||

[[Category:Hardware]] | [[Category:Hardware]] | ||

Latest revision as of 12:47, 12 April 2012

Contents

Introduktion af Hardware Interrupts

Når ydre enheder er klar til at aflevere eller modtage data, er det oftest CPU’ens opgave at modtage eller sende dette. Dette kunne for eksempel være et tastaturtryk der skal overføres til et program. Dette kan principielt foregå på to måder.

Uden interrupt

- CPU’en spørger med intervaller om ydre enheder har brug for CPU’ens service. Dette kaldes at polle ydre enheder. Dette princip bevirker at CPU’en bruger overflødig tid, på for eksempel at "polle" tastaturet om der er trykket på en tast.

| Ved pollning af flere ydre enheder, kan softwaren nemt blive meget rodet | |

| Bemærk |

Med interrupt

- Interrupt drevet. Dette bevirker at CPU’en arbejder uforstyrret af ydre enheder, indtil en ydre enhed ønsker at blive serviceret. Når en ydre enhed ønsker CPU’ens opmærksomhed afbryder den midlertidigt CPU’ens nuværende opgave, for at servicere den ydre enhed. Dette bevirker at CPU’en aflastes fra resultatløse forespørgsler til tastatur, mus, lydkort, harddisk, printer……

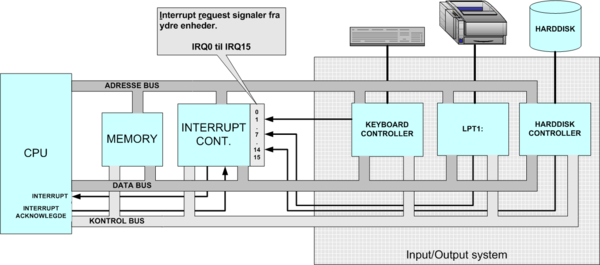

Når en ydre enhed ønsker at blive serviceret vil den sende et interruptsignal til den indbyggede interruptcontroller. Interruptcontrolleren har til opgave at sende et signal til CPU’en. CPU’en kan her efter, såfremt interrupt er enabled, sende et interrupt acknowlegde signal tilbage til interrupt controlleren som fortæller at interruptet accepteres. Interruptcontrolleren vil nu via databussen overføre interruptets vektornummer, hvorefter CPU’en vil springe til vektorens servicerutine.

Ved et tastaturtryk kunne følgende foregå

- (Sekvensen refererer til billedet ovenfor)

Der trykkes på tasten H

- Keyboard controllereren modtager H’et

- Keyboard controllereren sætter sit interrupt signal

- Interrupt controlleren modtager et IRQ-1

- Interrupt controlleren sætter sit interrupt signal for at varsko CPU’en

- CPU’en accepterer interruptet og sætter sit interrupt acknowlegde

- Interrupt controlleren fortæller via databussen at interruptet var IRQ-1

- CPU’en skifter til tastaturets service program

- CPU’en vender tilbage til programmet det kørte inden interruptet

Interrupt controllerens opbygning

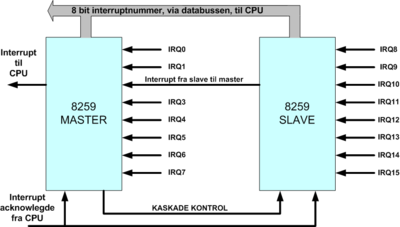

Interrupt controlleren var i den originale PC, med 8088 CPU, opbygget med en Intel 8259 interrupt controller integreret kreds som kan styre 8 hardwareinterrupts. Senere med PC/AT, blev interrupt systemet opbygget med to Intel 8259 kredse. Denne opbygning bruges stadig. Dog er interrupt controllerene indbygget i moderne chipsæt, og ikke som før som separate kredse.

Da CPU’en kun har to interrupt indgange, hvoraf den højst prioriterede er brugt til fejlsituationer, er der kun en interrupt indgang til to 8259 kredse. Derfor er det nødvendigt af kaskadekoble dem. Se billedet herunder.