Difference between revisions of "STM32F107VC/System architecture"

From Teknologisk videncenter

m |

m |

||

| Line 3: | Line 3: | ||

The [[STM32F107VC]] is a ''connectivity line device'' with the basic architecture shown to the right. | The [[STM32F107VC]] is a ''connectivity line device'' with the basic architecture shown to the right. | ||

* Five masters: | * Five masters: | ||

| − | **Cortex™-M3 core DCode bus (D-bus) | + | **Cortex™-M3 core |

| + | ** DCode bus (D-bus) | ||

| + | **System bus (S-bus) | ||

**GP-DMA1 & 2 (general-purpose DMA) | **GP-DMA1 & 2 (general-purpose DMA) | ||

**Ethernet DMA | **Ethernet DMA | ||

Revision as of 07:08, 3 September 2011

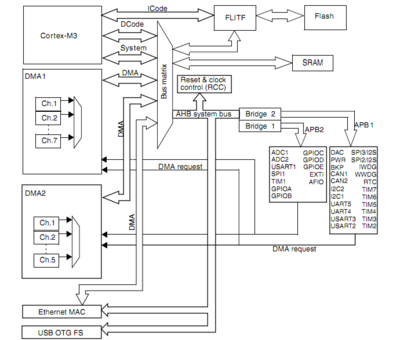

The STM32F107VC is a highly complex device. To understand the device it's necessary first to understand the basic system architecture. Se Chapter 3 in the Reference Manual.

The STM32F107VC is a connectivity line device with the basic architecture shown to the right.

- Five masters:

- Cortex™-M3 core

- DCode bus (D-bus)

- System bus (S-bus)

- GP-DMA1 & 2 (general-purpose DMA)

- Ethernet DMA

- Three slaves:

- Internal SRAM

- Internal Flash memory

- AHB to APB bridges (AHB to APBx), which connect all the APB peripherals