STM32F107VC/RCC

From Teknologisk videncenter

RCC - reset and clock control

STM32F107VC is a Connectivity Line Device and this register refers to Chapter 8 in The Reference manual.

Reset

There are three tyoes of reset

- System Reset

- Power Reset

- Backup Domain Reset

Se section 8.1 of the The Reference manual for further information.

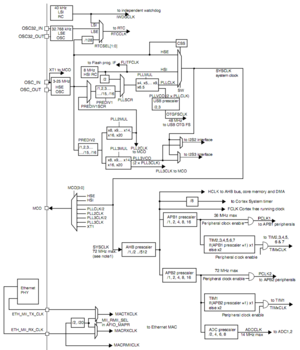

Clocks

Three different clock sources can be used to drive the system clock (SYSCLK):

- HSI oscillator clock

- HSE oscillator clock

- PLL clock

Clock Paths

- The SYSCLK and Cortex M3 Clock can be configured in five different paths. See Clock Paths

HSI - High Speed Internal Clock

The HSI clock signal is generated from an internal 8 MHz RC Oscillator and can be used directly as a system clock or divided by 2 to be used as PLL input.

| Name | Section | Name | r/w | Bits | Function |

|---|---|---|---|---|---|

| RCC_RC | 8.3.1 | Clock Control Register | rw/r | HSICAL[7:0],HSITRIM[4:0] HSIRDY,HSION | HSI ON and calibration |

HSE - High Speed External clock

The high speed external clock signal (HSE) can be generated from two possible clock sources:

- HSE external crystal/ceramic resonator

- HSE user external clock

The MCBSTM32C evaluation board has a 25Mhz on board crystal for HSE Clock.

PLL - Phase Locked Loops

The main PLL provides a frequency multiplier starting from one of the following clock sources:

- HSI clock divided by 2

- HSE or PLL2 clock through a configurable divider